[Solved]Given Homework Processor Hrre Capable Addressing 32 8 Bit 1 Byte Wide Registers However 29 Q37048869

Please answer all parts.

Thank you!!

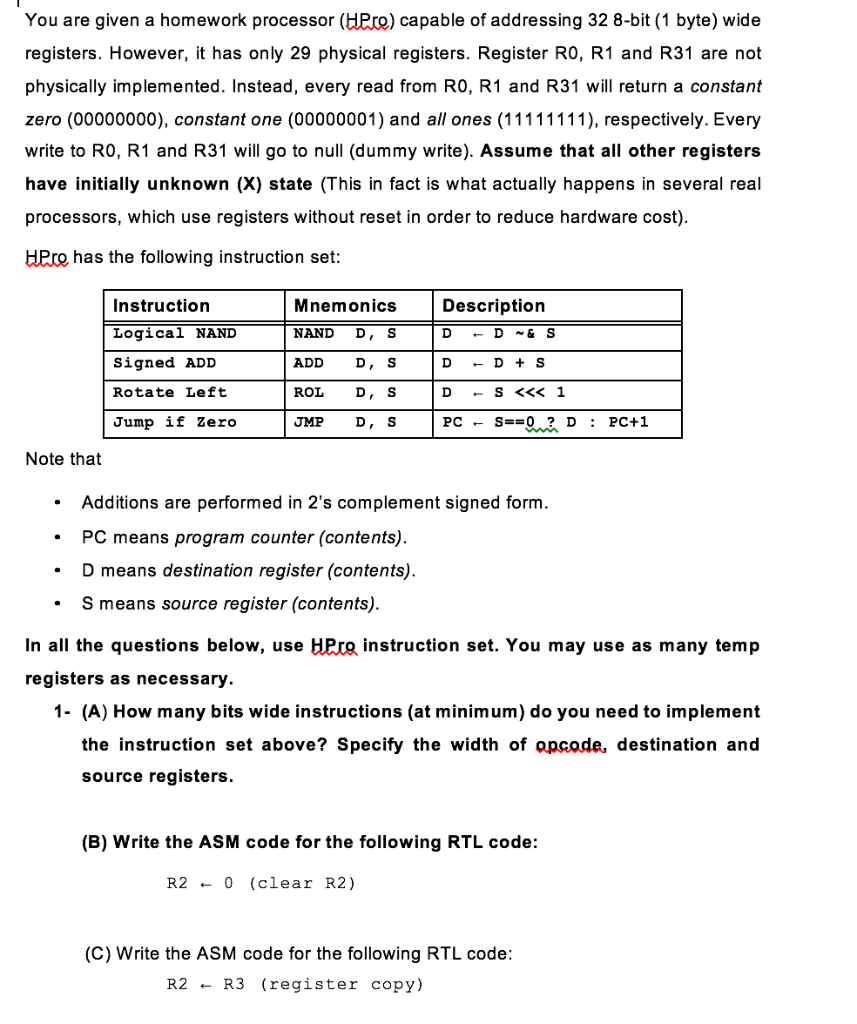

You are given a homework processor (HRre) capable of addressing 32 8-bit (1 byte) wide registers. However, it has only 29 physical registers. Register RO, R1 and R31 are not physically implemented. Instead, every read from RO, R1 and R31 will return a constant zero (00000000), constant one (00000001) and all ones (11111111), respectively. Every write to RO, R1 and R31 will go to null (dummy write). Assume that all other registers have initially unknown (x) state (This in fact is what actually happens in several real processors, which use registers without reset in order to reduce hardware cost) HPro has the following instruction set Instruction Logical NAND Signed ADD Rotate Left Jump if Zero Mnemonics NANDD, S ADD ROL JMP Description D, S D, S D, S Note that Additions are performed in 2’s complement signed form PC means program counter (contents) D means destination register (contents) .S means source register (contents) In all the questions below, use HPre instruction set. You may use as many temp registers as necessary 1- (A) How many bits wide instructions (at minimum) do you need to implement the instruction set above? Specify the width of opcode, destination and source registers (B) Write the ASM code for the following RTL code: R20 (clear R2) (C) Write the ASM code for the following RTL code R2 – R3 (register copy) Show transcribed image text You are given a homework processor (HRre) capable of addressing 32 8-bit (1 byte) wide registers. However, it has only 29 physical registers. Register RO, R1 and R31 are not physically implemented. Instead, every read from RO, R1 and R31 will return a constant zero (00000000), constant one (00000001) and all ones (11111111), respectively. Every write to RO, R1 and R31 will go to null (dummy write). Assume that all other registers have initially unknown (x) state (This in fact is what actually happens in several real processors, which use registers without reset in order to reduce hardware cost) HPro has the following instruction set Instruction Logical NAND Signed ADD Rotate Left Jump if Zero Mnemonics NANDD, S ADD ROL JMP Description D, S D, S D, S Note that Additions are performed in 2’s complement signed form PC means program counter (contents) D means destination register (contents) .S means source register (contents) In all the questions below, use HPre instruction set. You may use as many temp registers as necessary 1- (A) How many bits wide instructions (at minimum) do you need to implement the instruction set above? Specify the width of opcode, destination and source registers (B) Write the ASM code for the following RTL code: R20 (clear R2) (C) Write the ASM code for the following RTL code R2 – R3 (register copy)

Expert Answer

Answer to You are given a homework processor (HRre) capable of addressing 32 8-bit (1 byte) wide registers. However, it has only 2… . . .

OR