[Solved]1 Draw Synthesized Logic Resulting Following Vhdl Code Label Signals Diagram Precisely Ent Q37231945

problem 1

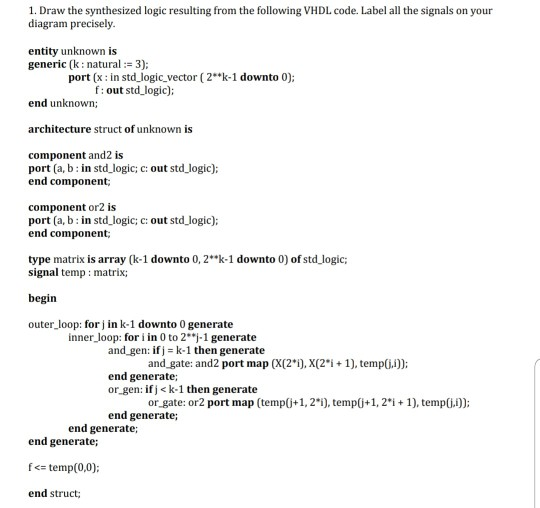

1. Draw the synthesized logic resulting from the following VHDL code. Label all the signals on your diagram precisely entity unknown is generic (k: natural 3); port (x: in std_logic_vector (2″k-1 downto 0): f: out std_logic): end unknown; architecture struct of unknown is component and2 is port (a, b: in std_logic; c: out std_logic) end component; component or2 is port (a, b: in std_logic; c: out std_logic) end component type matrix is array (k-1 downto 0, 2″k-1 downto 0) of std logic; signal temp: matrix; begin outer_loop: for j in k-1 downto 0 generate inner_loop: for i in 0 to 2″j-1 generate and gen: ifj k-1 then generate and gate: and2 port map (X(2*i), X(2″1), temp) end generate; or gen: if j <k-1 then generate or gate: or2 port map (tempG+1,2″i), temp+1,2i1), temp) end generate; end generate; end generate; fc= temp(0,0) end struct Show transcribed image text 1. Draw the synthesized logic resulting from the following VHDL code. Label all the signals on your diagram precisely entity unknown is generic (k: natural 3); port (x: in std_logic_vector (2″k-1 downto 0): f: out std_logic): end unknown; architecture struct of unknown is component and2 is port (a, b: in std_logic; c: out std_logic) end component; component or2 is port (a, b: in std_logic; c: out std_logic) end component type matrix is array (k-1 downto 0, 2″k-1 downto 0) of std logic; signal temp: matrix; begin outer_loop: for j in k-1 downto 0 generate inner_loop: for i in 0 to 2″j-1 generate and gen: ifj k-1 then generate and gate: and2 port map (X(2*i), X(2″1), temp) end generate; or gen: if j

Expert Answer

Answer to 1. Draw the synthesized logic resulting from the following VHDL code. Label all the signals on your diagram precisely en… . . .

OR