[Solved]-Question 1 Computer Uses Ram Chip 128×8 Rom Chip 512×8 Intend Interface Six Ram Chips Two Q37266842

solve all please

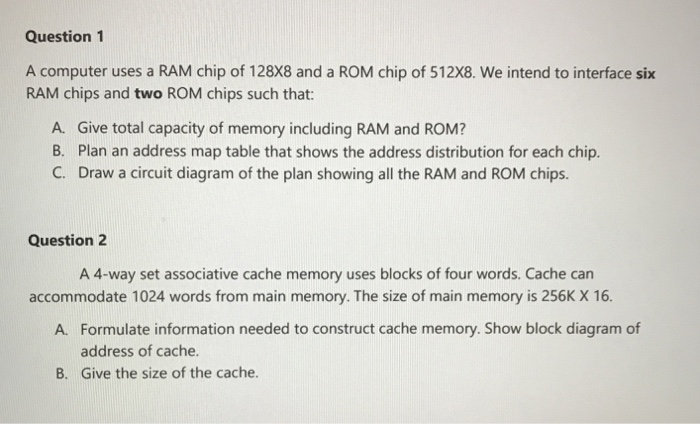

Question 1 A computer uses a RAM chip of 128X8 and a ROM chip of 512X8. We intend to interface six RAM chips and two ROM chips such that: A. B. C. Give total capacity of memory including RAM and ROM? Plan an address map table that shows the address distribution for each chip. Draw a circuit diagram of the plan showing all the RAM and ROM chips. Question2 A 4-way set associative cache memory uses blocks of four words. Cache can A. Formulate information needed to construct cache memory. Show block diagram of B. Give the size of the cache. accommodate 1024 words from main memory. The size of main memory is 256K X 16. address of cache Question 3 The access time of a cache is 80 ns and the access time of main memory is 1200 ns. We have 85% of instructions are directed to read while 15% is for writes. Hit ratio is 92%. A write through procedure is used. A. Give the average access time considering only the read requests B. Give average access time for both read and write requests C. Give the overall hit ratio given the write cycle as well. Question 4 A digital computer has a memory of 32K X 16 and a cache memory of 2K (2048) words. The cache uses a direct mapping with block size of eight word. How many bits are there in tag, index, blocks, and word fields of address format? How many bits are there in each word of the cache? Show division of functions and include valid bit. A. B. C. The cache has how many blocks? Show transcribed image text Question 1 A computer uses a RAM chip of 128X8 and a ROM chip of 512X8. We intend to interface six RAM chips and two ROM chips such that: A. B. C. Give total capacity of memory including RAM and ROM? Plan an address map table that shows the address distribution for each chip. Draw a circuit diagram of the plan showing all the RAM and ROM chips. Question2 A 4-way set associative cache memory uses blocks of four words. Cache can A. Formulate information needed to construct cache memory. Show block diagram of B. Give the size of the cache. accommodate 1024 words from main memory. The size of main memory is 256K X 16. address of cache

Question 1 A computer uses a RAM chip of 128X8 and a ROM chip of 512X8. We intend to interface six RAM chips and two ROM chips such that: A. B. C. Give total capacity of memory including RAM and ROM? Plan an address map table that shows the address distribution for each chip. Draw a circuit diagram of the plan showing all the RAM and ROM chips. Question2 A 4-way set associative cache memory uses blocks of four words. Cache can A. Formulate information needed to construct cache memory. Show block diagram of B. Give the size of the cache. accommodate 1024 words from main memory. The size of main memory is 256K X 16. address of cache Question 3 The access time of a cache is 80 ns and the access time of main memory is 1200 ns. We have 85% of instructions are directed to read while 15% is for writes. Hit ratio is 92%. A write through procedure is used. A. Give the average access time considering only the read requests B. Give average access time for both read and write requests C. Give the overall hit ratio given the write cycle as well. Question 4 A digital computer has a memory of 32K X 16 and a cache memory of 2K (2048) words. The cache uses a direct mapping with block size of eight word. How many bits are there in tag, index, blocks, and word fields of address format? How many bits are there in each word of the cache? Show division of functions and include valid bit. A. B. C. The cache has how many blocks? Show transcribed image text Question 1 A computer uses a RAM chip of 128X8 and a ROM chip of 512X8. We intend to interface six RAM chips and two ROM chips such that: A. B. C. Give total capacity of memory including RAM and ROM? Plan an address map table that shows the address distribution for each chip. Draw a circuit diagram of the plan showing all the RAM and ROM chips. Question2 A 4-way set associative cache memory uses blocks of four words. Cache can A. Formulate information needed to construct cache memory. Show block diagram of B. Give the size of the cache. accommodate 1024 words from main memory. The size of main memory is 256K X 16. address of cache

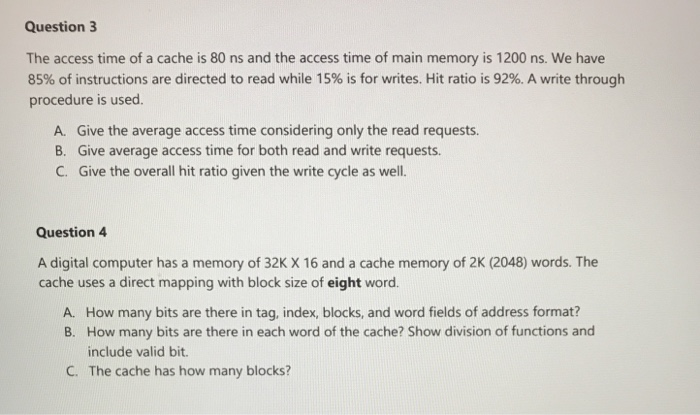

Question 3 The access time of a cache is 80 ns and the access time of main memory is 1200 ns. We have 85% of instructions are directed to read while 15% is for writes. Hit ratio is 92%. A write through procedure is used. A. Give the average access time considering only the read requests B. Give average access time for both read and write requests C. Give the overall hit ratio given the write cycle as well. Question 4 A digital computer has a memory of 32K X 16 and a cache memory of 2K (2048) words. The cache uses a direct mapping with block size of eight word. How many bits are there in tag, index, blocks, and word fields of address format? How many bits are there in each word of the cache? Show division of functions and include valid bit. A. B. C. The cache has how many blocks?

Expert Answer

Answer to Question 1 A computer uses a RAM chip of 128X8 and a ROM chip of 512X8. We intend to interface six RAM chips and two ROM… . . .

OR