[Solved] Exercise Examine Data Dependences Affect Execution Basic 5 Stage Pipeline Described Sectio Q37247477

In this exercise, we examine how data dependences affectexecution in the basic 5-stage pipeline described in Section 4.5.Problems in this exercise refer to the following sequence ofinstructions: SUB R3,R1,R2 ADD R2,R3,R2 XOR R3,R3,R2 Also, assumethe following cycle times for each of the options related toforwarding. Without forwarding, there is no additional forwardingpaths. Note that a new value can be written into a register in thefirst half of a clock cycle and this value can be read from thesame register in the second half of a clock cycle. Full forwardingmeans the pipeline has two forwarding paths: from EX/MEM to EX(also called ALU-ALU forwarding), and from MEM/WB to EX. 1.1)Indicate dependences and their type (RAW, WAR, WAW, RAR). [Hint:For example, there is a RAW (read-after-write) on r2 from I2 toI3.] 1.2) Assume that there is no forwarding in this pipelinedprocessor. Please add nop instructions to ensure correctness. 1.3)Assume that there is full forwarding. Please add nop instructionsto ensure correctness. 1.4) What is the total execution time (inwall clock time) of this instruction sequence without forwardingand with full forwarding? What is the speedup achieved by addingfull forwarding to a pipeline that had no forwarding?

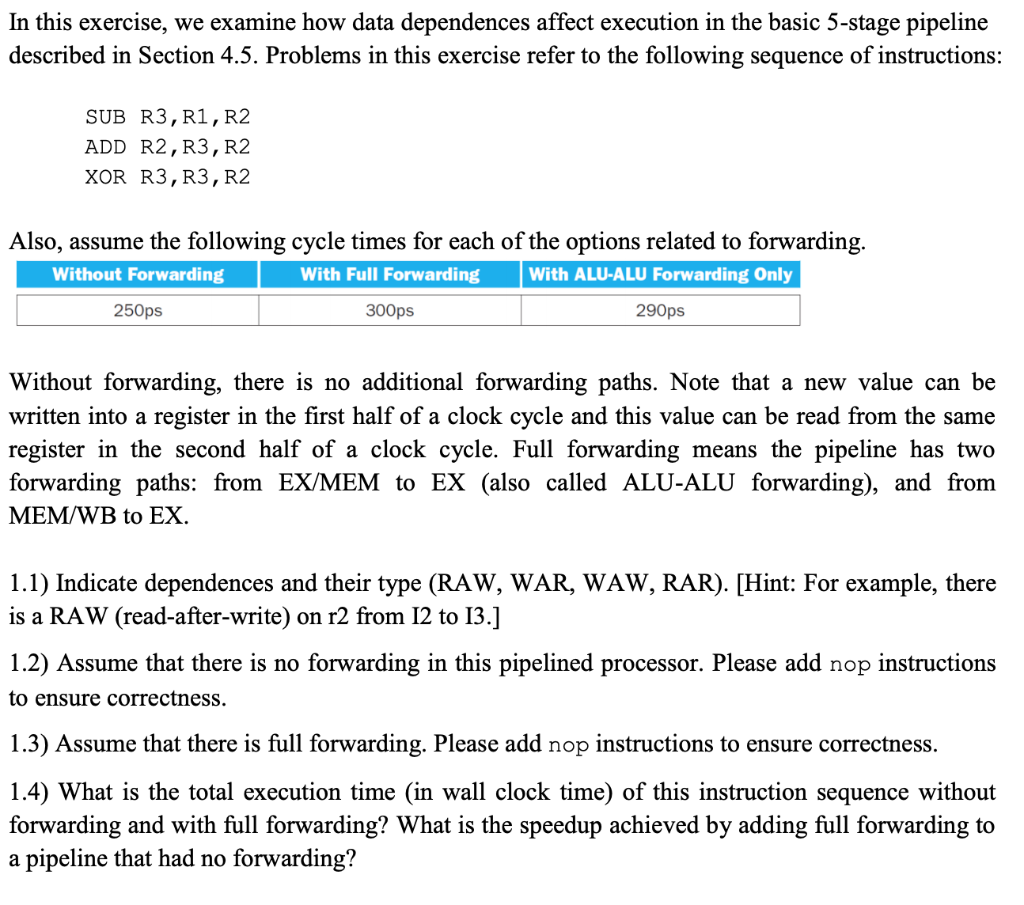

In this exercise, we examine how data dependences affect execution in the basic 5-stage pipeline described in Section 4.5. Problems in this exercise refer to the following sequence of instructions: SUB R3,R1,R2 ADD R2, R3, R2 XOR R3,R3, R2 Also, assume the following cycle times for each of the options related to forwarding. Without Forwarding With Full Forwarding With ALU-ALU Forwarding Only 300ps 250ps 290ps Without forwarding, there is no additional forwarding paths. Note that a new value can be written into a register in the first half of a clock cycle and this value can be read from the same register in the second half of a clock cycle. Full forwarding means the pipeline has two forwarding paths: from EX/MEM to EX (also called ALU-ALU forwarding), and from MEM/WB to EX 1.1) Indicate dependences and their type (RAW, WAR, WAW, RAR). [Hint: For example, there is a RAW (read-after-write) on r2 from 12 to I3.] 1.2) Assume that there is no forwarding in this pipelined processor. Please add nop instructions to ensure correctness. 1.3) Assume that there is full forwarding. Please add nop instructions to ensure correctness. 1.4) What is the total execution time (in wall clock time) of this instruction sequence without forwarding and with full forwarding? What is the speedup achieved by adding full forwarding to a pipeline that had no forwarding? Show transcribed image text In this exercise, we examine how data dependences affect execution in the basic 5-stage pipeline described in Section 4.5. Problems in this exercise refer to the following sequence of instructions: SUB R3,R1,R2 ADD R2, R3, R2 XOR R3,R3, R2 Also, assume the following cycle times for each of the options related to forwarding. Without Forwarding With Full Forwarding With ALU-ALU Forwarding Only 300ps 250ps 290ps Without forwarding, there is no additional forwarding paths. Note that a new value can be written into a register in the first half of a clock cycle and this value can be read from the same register in the second half of a clock cycle. Full forwarding means the pipeline has two forwarding paths: from EX/MEM to EX (also called ALU-ALU forwarding), and from MEM/WB to EX 1.1) Indicate dependences and their type (RAW, WAR, WAW, RAR). [Hint: For example, there is a RAW (read-after-write) on r2 from 12 to I3.] 1.2) Assume that there is no forwarding in this pipelined processor. Please add nop instructions to ensure correctness. 1.3) Assume that there is full forwarding. Please add nop instructions to ensure correctness. 1.4) What is the total execution time (in wall clock time) of this instruction sequence without forwarding and with full forwarding? What is the speedup achieved by adding full forwarding to a pipeline that had no forwarding?

Expert Answer

Answer to In this exercise, we examine how data dependences affect execution in the basic 5-stage pipeline described in Section 4…. . . .

OR